- 您现在的位置:买卖IC网 > Sheet目录2003 > LTC1298IS8#TRPBF (Linear Technology)IC A/D CONV SAMPLING 12BIT 8SOIC

8

LTC1286/LTC1298

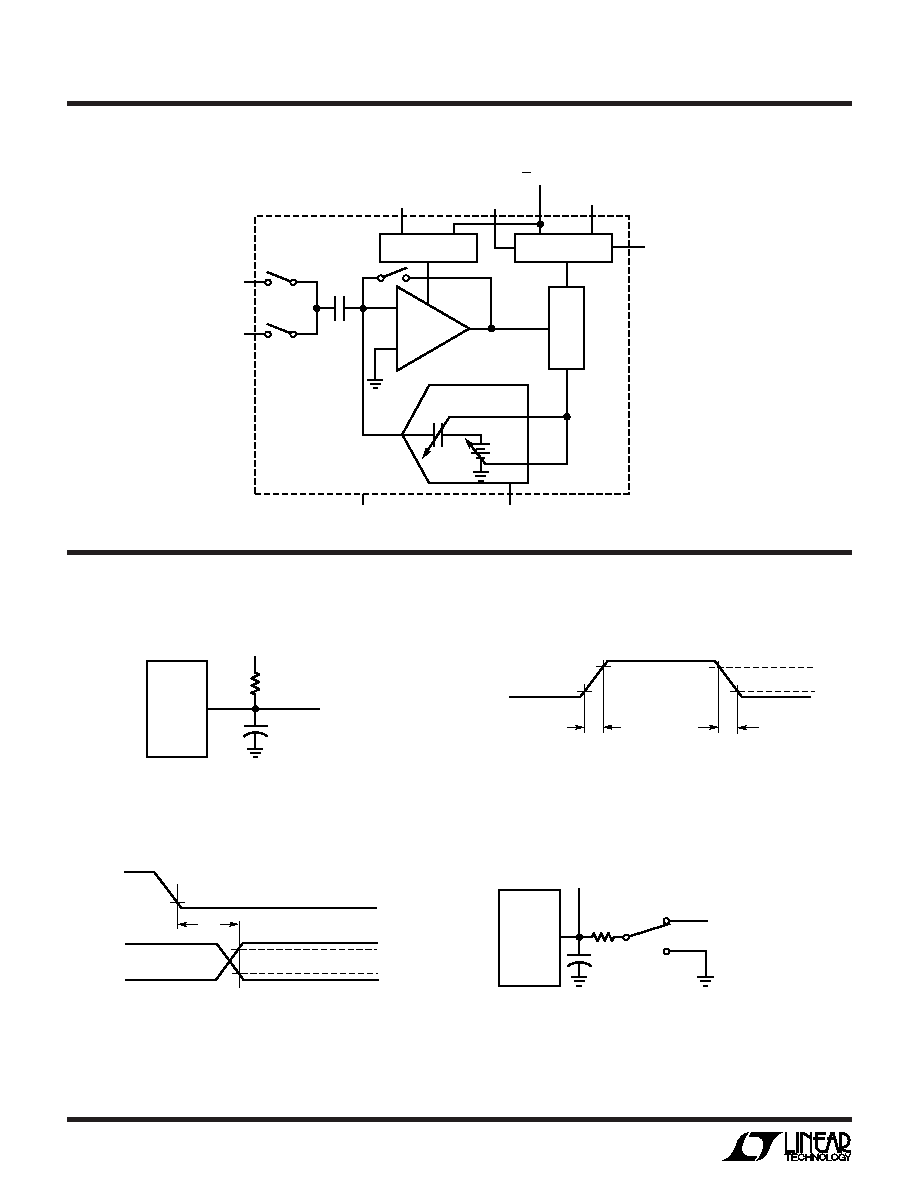

BLOCK DIAGRAM

W

–

+

CSAMPLE

VCC (VCC/VREF)

CS/SHDN

CLK

DOUT

IN+ (CH0)

IN– (CH1)

MICROPOWER

COMPARATOR

CAPACITIVE DAC

VREF

GND

PIN NAMES IN PARENTHESES

REFER TO THE LTC1298

(DIN)

BIAS AND

SHUTDOWN CIRCUIT

SAR

SERIAL PORT

TEST CIRCUITS

DOUT

1.4V

3k

100pF

TEST POINT

LTC1286/98 TC01

DOUT

VOL

VOH

tr

tf

LTC1286/98 TC02

Voltage Waveforms for DOUT Rise and Fall Times, tr, tf

Load Circuit for tdDO, tr and tf

Load Circuit for tdis and ten

Voltage Waveforms for DOUT Delay Times, tdDO

CLK

DOUT

VIL

tdDO

VOL

VOH

LTC1286/98 TC03

DOUT

3k

100pF

TEST POINT

VCC tdis WAVEFORM 2, ten

tdis WAVEFORM 1

LTC1286/98 TC04

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC1327CNW#PBF

IC TXRX EIA/TIA-562 3.3V 28-DIP

LTC1329ACS8-50#TRPBF

IC D/A CONV 8BIT MICROPWR 8-SOIC

LTC1337CNW#PBF

IC 3DVR/5RCVR 5V RS232 28-DIP

LTC1382IN#PBF

IC TXRX 5V RS232 W/SHTDWN 18-DIP

LTC1383IS#TRPBF

IC TXRX 5V RS232 LOW PWR 16-SOIC

LTC1384IG#TRPBF

IC TXRX 5V RS232 LOW PWR 20-SSOP

LTC1385IN#PBF

IC TXRX 3.3V EIA/TIA-562 18-DIP

LTC1386IS#TRPBF

IC TXRX 3.3V EIA/TIA-562 16-SOIC

相关代理商/技术参数

LTC1298IS8PBF

制造商:Linear Technology 功能描述:12-Bit ADC uPower Sampling 2-Ch MUX SO8

LTC1314CS

功能描述:IC PCMCIA SWITCHNG MATRIX 14SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 电源分配开关 系列:- 特色产品:XRP252 Switches 标准包装:1 系列:- 类型:高端开关 输出数:2 Rds(开):140 毫欧 内部开关:是 电流限制:1.15A 输入电压:1.75 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN(3x3) 包装:Digi-Reel® 其它名称:1016-1691-6

LTC1314CS#PBF

功能描述:IC PCMCIA SWITCHNG MATRIX 14SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 电源分配开关 系列:- 特色产品:XRP252 Switches 标准包装:1 系列:- 类型:高端开关 输出数:2 Rds(开):140 毫欧 内部开关:是 电流限制:1.15A 输入电压:1.75 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN(3x3) 包装:Digi-Reel® 其它名称:1016-1691-6

LTC1314CS#TR

功能描述:IC SW MATRIX PCMCIA SGL 14SOIC RoHS:否 类别:集成电路 (IC) >> PMIC - 电源分配开关 系列:- 特色产品:XRP252 Switches 标准包装:1 系列:- 类型:高端开关 输出数:2 Rds(开):140 毫欧 内部开关:是 电流限制:1.15A 输入电压:1.75 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN(3x3) 包装:Digi-Reel® 其它名称:1016-1691-6

LTC1314CS#TRPBF

功能描述:IC PCMCIA SWITCHNG MATRIX 14SOIC RoHS:是 类别:集成电路 (IC) >> PMIC - 电源分配开关 系列:- 特色产品:XRP252 Switches 标准包装:1 系列:- 类型:高端开关 输出数:2 Rds(开):140 毫欧 内部开关:是 电流限制:1.15A 输入电压:1.75 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-WFDFN 裸露焊盘 供应商设备封装:10-TDFN(3x3) 包装:Digi-Reel® 其它名称:1016-1691-6

LTC1315CG#PBF

功能描述:IC PCMCIA SWITCHNG MATRIX 24SSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 电源分配开关 系列:- 标准包装:80 系列:- 类型:USB 开关 输出数:2 Rds(开):135 毫欧 内部开关:是 电流限制:1.5A 输入电压:2.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽)裸露焊盘 供应商设备封装:8-MSOP-PowerPad 包装:管件 配用:TPS2066-1EVM-296-ND - TPS2066-1EVM-296

LTC1315CG#TR

功能描述:IC SW MATRIX PCMCIA DUAL 24SSOP RoHS:否 类别:集成电路 (IC) >> PMIC - 电源分配开关 系列:- 标准包装:80 系列:- 类型:USB 开关 输出数:2 Rds(开):135 毫欧 内部开关:是 电流限制:1.5A 输入电压:2.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽)裸露焊盘 供应商设备封装:8-MSOP-PowerPad 包装:管件 配用:TPS2066-1EVM-296-ND - TPS2066-1EVM-296

LTC1315CG#TRPBF

功能描述:IC PCMCIA SWITCHNG MATRIX 24SSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 电源分配开关 系列:- 标准包装:80 系列:- 类型:USB 开关 输出数:2 Rds(开):135 毫欧 内部开关:是 电流限制:1.5A 输入电压:2.7 V ~ 5.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽)裸露焊盘 供应商设备封装:8-MSOP-PowerPad 包装:管件 配用:TPS2066-1EVM-296-ND - TPS2066-1EVM-296